# Thermal neutron induces Single-Event Upsets in the FPGA used in particle physics experiments

Chihiro Yamada <sup>1</sup>, Eitaro Hamada <sup>2</sup>, Kazuki Ueno <sup>12</sup>, Yu Nakazawa <sup>2</sup>

Osaka University <sup>1</sup>, High Energy Accelerator Research Organization (KEK) <sup>2</sup>

## Introduction

### Radiation on Particle Physics Experiments

To explore beyond the Standard Model, beams generated by accelerators are becoming **higher intensity, higher luminosity and higher energy**.

→ **increase background radiations**

(neutron, gamma, proton, etc.)

→ **affects electronics**.

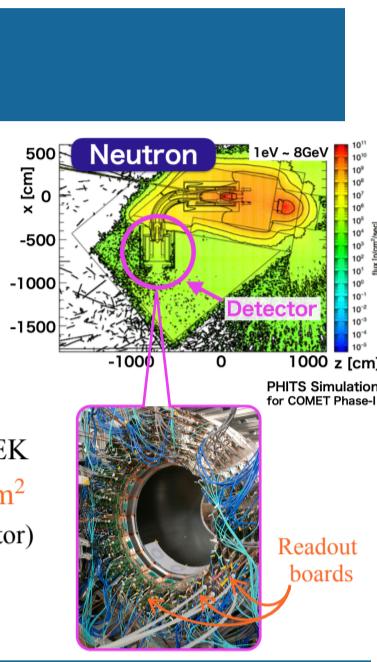

e.g.) COMET <sup>[1]</sup> @ J-PARC, SuperKEKB/Belle II <sup>[2]</sup> @ KEK

Estimated cumulative neutron dose  $\sim 10^{12} \text{ n}_{1-\text{MeV eq}}/\text{cm}^2$

(Including safety factor)

There is a large amount of **thermal neutrons** around the detector readout electronics.

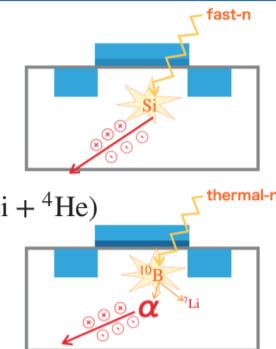

### Neutron effect

• Fast neutron ( $> 0.1 \text{ MeV}$ ): nuclear reaction with Si

→ **emit Ion particle**

• Thermal neutron ( $< 1 \text{ eV}$ ): capture reaction with  $^{10}\text{B}$

→ **emit  $\alpha$  particle** ( $^{10}\text{B} + \text{n} \rightarrow ^7\text{Li} + ^4\text{He}$ )

→ Induce electron-hole pairs

→ **Change the logic state (Single-Event Upset, SEU)**

Counterplan: neutron shield, error-correcting code, etc.

### Semiconductor design & SEU occurred by thermal neutron

Trend:  $^{10}\text{B}$  less oxide film is used → SEUs by thermal neutron decreased...?

→ Some studies reported SEUs induced by thermal neutrons [3], [4].

It might still contain  $^{10}\text{B}$ ? / SEU trends vary depending on the product type.

### Motivation of this study

To estimate SEUs caused by thermal neutrons in an FPGA

(For fast neutrons, it has been studied in [5].)

## Result & Discussion

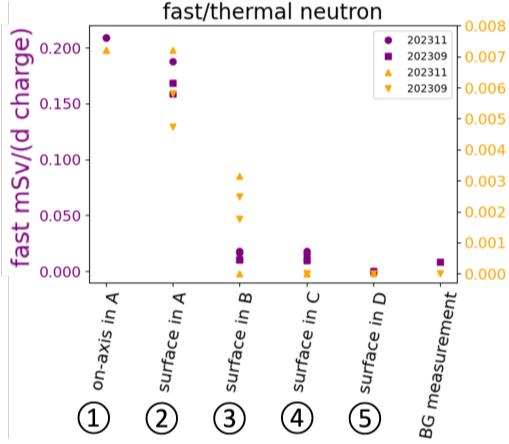

### Neutron measurement

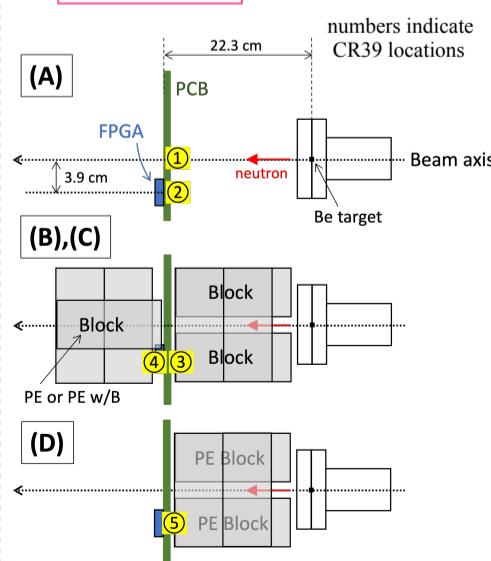

- Without blocks, both fast and thermal neutrons were irradiated. (1, 2)

- The one-minute measurement in 202309-thermal (▲) was too short to detect in (3).

- Thermal and fast neutrons are successfully shielded in (4) due to  $\text{B}_2\text{O}_3$ -containing blocks.

- Most thermal neutrons came from the reflection of the behind block in (5) compare to (3).

→ Confirmed neutron energy trend

A : fast, thermal

B : thermal

C : neither fast nor thermal

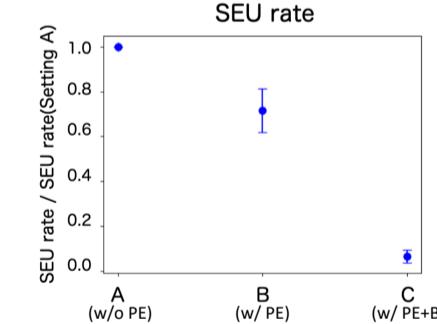

### SEU measurement

| Setup | SEU count | deutron charge[C] | SEU / (d charge)     |

|-------|-----------|-------------------|----------------------|

| A     | 113       | $4.9 \times 10^3$ | $2.3 \times 10^{-2}$ |

| B     | 104       | $6.2 \times 10^3$ | $1.7 \times 10^{-2}$ |

| C     | 6         | $4.0 \times 10^3$ | $1.5 \times 10^{-3}$ |

SEU counts increased in proportion to the beam charge →

← The SEU rate on each setups relative to the result of A

★ It was found that SEUs occurred due to thermal neutrons.

★ Shielding of  $\text{B}_2\text{O}_3$ -containing blocks greatly contributes to reducing the SEUs.

## Conclusion & Future

- Particle physics experiments using the beam of high-intensity, luminosity, and energy require consideration of radiation effects on electronics.

- Fast neutrons and thermal neutrons can induce charged particles inside transistors through different processes, which can cause SEUs.

- We investigated SEUs induced by thermal neutrons using an FPGA employed in a particle experiment.

- By placing polyethylene blocks, we succeeded in producing thermal neutrons from a tandem accelerator and observed SEUs caused by thermal neutrons.

- We showed that it is necessary to consider the influence of thermal neutrons in the experiments and the usefulness of countermeasures such as shielding.

### Future work

- To better understand the rate of SEU

- ★ Simulating a detailed neutron energy distribution

- ★ Measuring the energy

- Investigate where and how much  $^{10}\text{B}$  is contained by elemental analysis

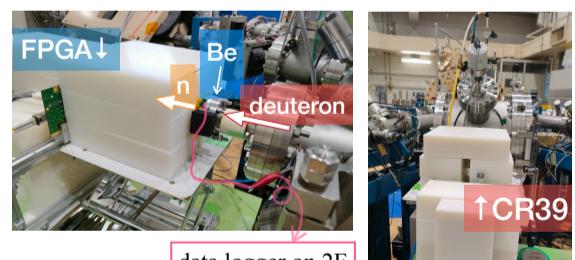

### (A) : Without blocks (reference)

CR39 - ① On-axis, ② FPGA surface

### (B) : With Polyethylene (PE) blocks (degrade or reflect fast neutrons)

CR39 - ③ FPGA surface

### (C) : With PE blocks containing $\text{B}_2\text{O}_3$ (shield both fast and thermal neutrons)

CR39 - ④ FPGA surface

### (D) : Remove blocks behind FPGA from (B) (investigate the impact of behind block = reflected-derived thermal neutrons)

CR39 - ⑤ FPGA surface

Background (BG) CR39 - no irradiation

## Acknowledgement

This work was supported by World Premier International Research Center Initiative (WPI), MEXT, Japan. The authors would like to express their sincere thanks to the staffs of The Tandem Accelerator Laboratory of Kobe University.

## Reference

- G. Adamov, et al., Prog. Theor. Exp. Phys. 033C01, (2020)

- Abe T, et al., arXiv:1011.0352 (2010)

- H. Iwashita, et al., IEEE Trans Nucl Sci., **70**, 216-221, (2023)

- M. Cecchetto, et al., IEEE Trans Nucl Sci., **67**, 1412-1420, (2020)

- Y. Nakazawa, et al., Nucl. Instrum. Meth. A, **936**, 351-352(2019)

- K. Ueno, et al., Nucl. Instrum. Meth. A, **936**, 298-299, (2019)

- Nagase Landauer Ltd., "Luminescence Badge (for neutron) Catalog"

- AMD Inc., "Soft Error Mitigation Controller" (PG036)